前言

在半導體製造與SMT組裝中,封裝不僅僅是保護措施——它直接影響生產良率、送料穩定性與元件可靠性。晶片載帶是一種專為積體電路(IC)與高價值半導體元件設計的專用載帶,其精度與一致性至關重要。

不同於用於被動元件的一般用途載帶,晶片載帶必須符合更嚴格的尺寸公差要求,提供可靠的靜電放電(ESD)保護,並確保在高速貼裝條件下穩定送料。即使是細微的設計不匹配,也可能導致晶片旋轉、取放錯誤或靜電損傷等問題。

了解晶片載帶的運作原理——以及如何選擇合適的規格配置——對於致力於降低缺陷率並提升SMT效率的工程師、採購團隊與封裝專業人員而言至關重要。

什麼是晶片載帶及其運作原理

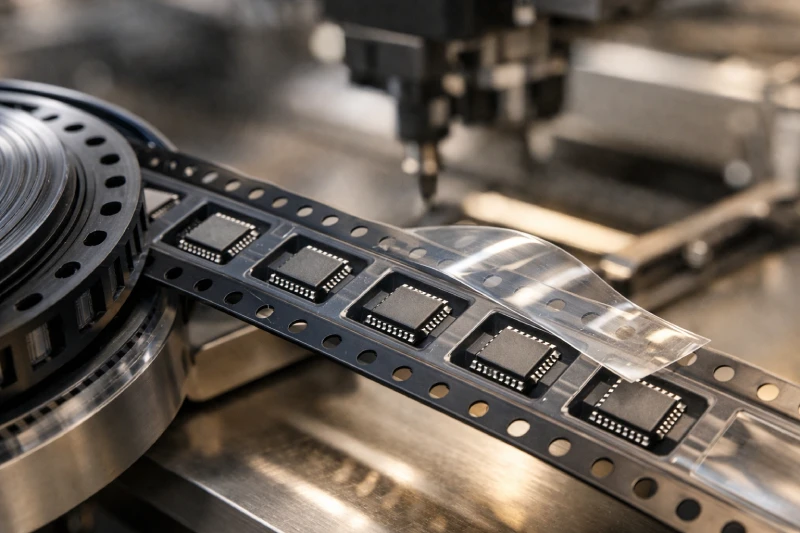

晶片載帶是一種精密工程化封裝載體,用於在編帶與捲盤系統中儲存、保護及運輸半導體元件。其廣泛應用於自動化SMT組裝,在高速條件下將元件送入取放機。

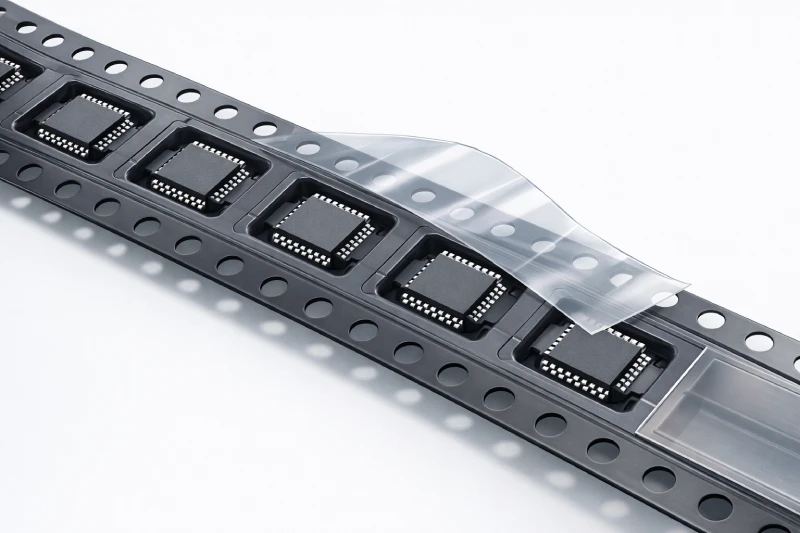

該載帶由以下幾個關鍵結構要素組成:

- 承載腔(cavities): 設計用於安全固定單顆晶片

- 節距(Pitch): 承載腔之間的間距,確保同步送料

- 齒孔(Sprocket holes): 供送料器進行定位與帶動載帶前進

- 上蓋帶(Cover tape): 封裝並固定元件,於運輸過程中提供保護

在典型流程中,元件被裝入口袋內,經上蓋帶封合後捲繞於捲盤上。在SMT組裝過程中,送料器向前拉動載帶並同步剝離上蓋帶,使取放頭能夠逐一取出元件。

相較於標準 載帶,晶片載帶具備更嚴格的口袋公差與強化的材料特性,以防止元件移動、翻轉或受損——特別是對於精密IC封裝。

晶片載帶的關鍵設計參數

晶片載帶的性能取決於其設計精度。幾何或材料的微小變化,都可能顯著影響送料穩定性與元件完整性。

口袋尺寸與公差

口袋設計必須與晶片尺寸緊密匹配,包括長度、寬度與厚度。間隙過大可能導致旋轉或偏移;間隙不足則可能造成卡料或難以取件。

關鍵考量包括:

- 受控間隙以防止位移

- 一致的承載腔深度以利真空吸取

- 平滑的腔體表面以避免機械應力

對於QFN或BGA等複雜封裝外形,製造商通常採用 壓紋載帶 以實現精確的腔體形狀。

節距精度與送料穩定性

節距精度決定載帶在SMT送料器中前進的可靠性。任何節距偏差都可能導致口袋與取件位置錯位。

在高速組裝環境(例如每小時超過60,000個元件)下,即使微小的節距誤差也可能導致:

- 吸取失敗

- 設備停機次數增加

- 貼裝精度降低

維持嚴格的節距公差可確保平穩且不中斷的送料。

材料選擇(PS、PET、PC)

材料選擇會影響機械強度、透明度、耐熱性與ESD特性。

- 聚苯乙烯(PS): 具成本效益,適用於標準IC封裝

- 聚對苯二甲酸乙二酯(PET): 透明,適用於光學檢測系統

- 聚碳酸酯(PC): 具高耐溫性,適用於嚴苛環境

選擇合適材料需根據元件敏感度、製程條件與檢測需求而定。

半導體晶片的ESD與防潮保護

半導體元件對靜電放電極為敏感。即使是低電壓ESD事件,也可能造成難以在檢測中發現的潛在缺陷,並最終導致客戶端失效。

晶片載帶透過以下方式加以防護:

- 導電材料: 提供可控制的靜電釋放路徑

- 抗靜電塗層: 在操作過程中防止電荷累積

這些解決方案通常整合於 防靜電載帶 配置中。

濕氣敏感等級考量

許多IC封裝被歸類為濕氣敏感等級(MSL)元件,意味著其會從環境中吸收濕氣。不當處理可能導致:

- 回流焊過程中的爆米花效應

- 內部結構損傷

- 器件可靠性降低

載帶需與乾燥包裝、乾燥劑及防潮袋配合使用,以在儲存與運輸過程中保護敏感元件。

晶片載帶應用中的常見問題

即使採用高品質材料,不當的設計或選型仍可能導致反覆出現的生產問題。了解這些問題有助於找出根本原因並防止良率損失。

晶片旋轉或偏移

口袋尺寸過大或腔體幾何設計不佳,可能使晶片在口袋內旋轉或位移,導致取件方向錯誤與貼裝偏差。

SMT設備中的送料問題

送料不穩通常由以下原因造成:

- 節距間距不一致

- 齒孔錯位

- 載帶變形

這些問題會破壞送料器與貼裝頭之間的同步。

上蓋帶剝離問題

剝離力必須精確控制。過大可能導致元件被帶起或位移;過小則會影響封合完整性。

剝離不穩可能導致:

- 元件遺失

- 高速運行時元件飛散

- 停機時間增加

靜電損傷(ESD失效)

若缺乏適當的ESD保護,晶片可能發生初期檢測無法發現但在客戶端失效的隱性損傷。

當標準解決方案無法解決上述問題時,許多製造商會採用 客製化載帶 設計,以優化口袋幾何、材料與整體性能。

標準與客製化晶片載帶:何時選擇各類型

在標準與客製化載帶之間的選擇,取決於元件類型、生產量與品質要求。

標準載帶

- 成本較低且交期較快

- 適用於廣泛使用的封裝(例如:SOP、SOT)

- 適用於一般用途應用

客製化載帶

- 為特殊或高價值元件設計

- 優化的承載腔尺寸與公差

- 提升送料可靠性並降低缺陷率

對於QFN、BGA或不規則形狀IC等先進半導體封裝,客製化方案尤為重要。

如何選擇合適的晶片載帶(逐步說明)

選擇合適的晶片載帶需依循結構化評估流程。

步驟1:定義元件尺寸

精確測量長度、寬度、厚度及允許公差,以確保口袋設計適當並防止位移。

步驟2:確定材料需求

請考量:

- ESD敏感性

- 檢測所需透明度

- 耐熱性

步驟3:匹配封裝類型

不同封裝類型需要不同的口袋幾何設計。例如:

- 扁平封裝需要較淺的承載腔

- 球柵陣列需要較深的腔體

步驟4:驗證剝離力

確保上蓋帶剝離在各種生產條件下均保持穩定一致,這將直接影響送料性能。

步驟5:進行試產測試

在全面量產前,應於實際SMT條件下測試載帶,評估:

- 送料順暢度

- 吸取精度

- 缺陷率

與提供整合式 編帶與捲盤封裝解決方案 的供應商合作,可簡化驗證流程並降低導入風險。

晶片載帶產業標準(EIA-481說明)

EIA-481是規範電子元件編帶與捲盤封裝的主要產業標準,定義了關鍵參數,例如:

- 載帶寬度與承載腔尺寸

- 齒孔位置

- 捲盤尺寸與配置

符合EIA-481可確保與不同SMT設備及全球供應鏈之間的相容性,並在多供應商採購時降低整合問題。

對製造商與採購方而言,遵循此標準並非選項,而是維持一致品質與營運效率的必要條件。

結論:為何晶片載帶品質直接影響良率

晶片載帶的角色遠超過單純封裝,其直接影響元件在SMT組裝過程中的搬運、送料與貼裝方式。

口袋設計精度、材料選擇與ESD防護決定生產是順暢進行,還是反覆出現缺陷。不良設計的載帶可能導致偏移、送料錯誤與潛在可靠性風險。

對於高價值半導體元件而言,投資於經過工程設計的載帶解決方案,是降低缺陷、提升良率並確保產品長期可靠性的實務做法。