Introducción

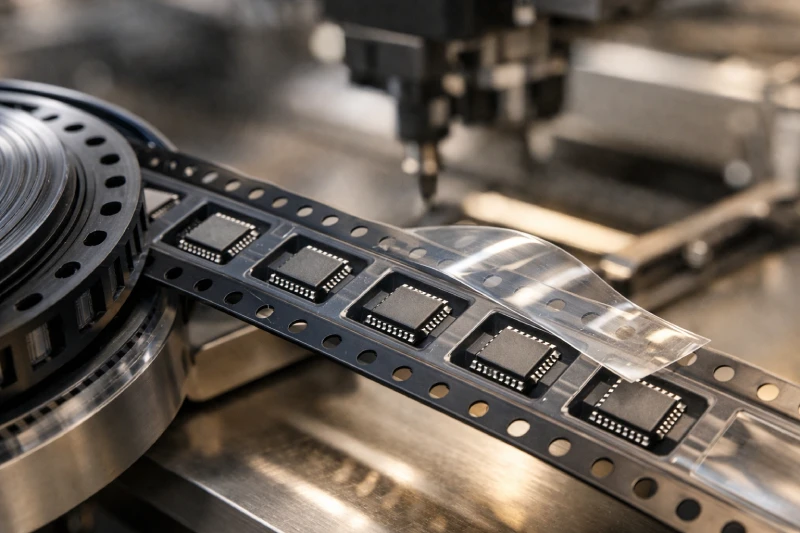

En la fabricación de semiconductores y el ensamblaje SMT, el embalaje no se limita a la protección: afecta directamente al rendimiento de producción, la estabilidad de alimentación y la fiabilidad de los componentes. La cinta portadora para chips es un tipo especializado de cinta portadora diseñada específicamente para circuitos integrados (IC) y componentes semiconductores de alto valor, donde la precisión y la consistencia son críticas.

A diferencia de las cintas de uso general empleadas para componentes pasivos, la cinta portadora para chips debe cumplir tolerancias dimensionales más estrictas, proporcionar una protección fiable contra descargas electrostáticas (ESD) y garantizar una alimentación estable a altas velocidades de colocación. Incluso pequeñas desviaciones de diseño pueden provocar problemas como rotación del chip, errores de pick-and-place o daños electrostáticos.

Comprender cómo funciona la cinta portadora para chips —y cómo seleccionar la configuración adecuada— es esencial para ingenieros, equipos de compras y especialistas en embalaje que buscan reducir defectos y mejorar la eficiencia en SMT.

Qué es la cinta portadora para chips y cómo funciona

La cinta portadora para chips es un medio de embalaje diseñado con precisión para almacenar, proteger y transportar componentes semiconductores dentro de sistemas de cinta y carrete. Se utiliza ampliamente en el ensamblaje SMT automatizado, donde los componentes se alimentan a máquinas pick-and-place a alta velocidad.

La cinta consta de varios elementos estructurales clave:

- Cavidades: Diseñadas para alojar de forma segura chips individuales

- Paso: La distancia entre cavidades, que garantiza una alimentación sincronizada

- Orificios de arrastre: Utilizados por los alimentadores para indexar y avanzar la cinta

- Cinta de cobertura: Sella los componentes en su posición y los protege durante el transporte

En un flujo de trabajo típico, los componentes se cargan en los alveolos, se sellan con cinta de cobertura y se enrollan en carretes. Durante el ensamblaje SMT, los alimentadores avanzan la cinta mientras retiran la cinta de cobertura, permitiendo que los cabezales pick-and-place recojan cada componente.

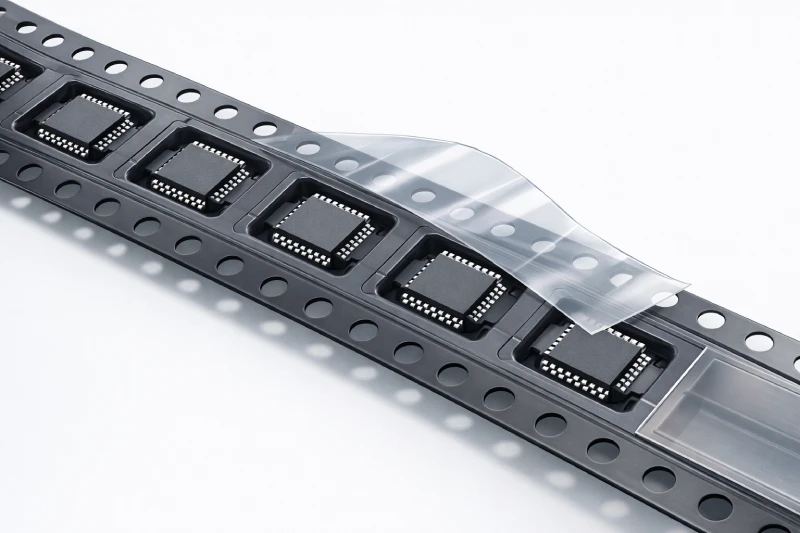

En comparación con la cinta portadora estándar, la cinta portadora para chips está diseñada con tolerancias de alveolo más estrictas y propiedades de material mejoradas para evitar movimiento, volteo o daños, especialmente en encapsulados IC delicados.

Parámetros clave de diseño de la cinta portadora para chips

El rendimiento de la cinta portadora para chips está definido por la precisión de su diseño. Pequeñas variaciones en la geometría o el material pueden afectar significativamente la estabilidad de alimentación y la integridad del componente.

Dimensiones del alveolo y tolerancias

El diseño del alveolo debe ajustarse estrechamente a las dimensiones del chip, incluyendo longitud, anchura y espesor. Un exceso de holgura puede provocar rotación o desalineación, mientras que una holgura insuficiente puede causar atascos o dificultades en la recogida.

Consideraciones clave incluyen:

- Holgura controlada para evitar movimientos

- Profundidad de cavidad uniforme para la recogida por vacío

- Superficies de cavidad lisas para evitar tensiones mecánicas

Para geometrías complejas, como encapsulados QFN o BGA, los fabricantes suelen recurrir a cinta portadora termoformada para lograr formas de cavidad precisas.

Precisión del paso y estabilidad de alimentación

La precisión del paso determina la fiabilidad con la que la cinta avanza a través de los alimentadores SMT. Cualquier desviación en el paso puede provocar desalineación entre el alveolo y la posición de recogida.

En entornos de ensamblaje de alta velocidad (por ejemplo, por encima de 60.000 componentes por hora), incluso ligeros errores de paso pueden provocar:

- Fallos de recogida

- Aumento de paradas de máquina

- Reducción de la precisión de colocación

Mantener tolerancias estrictas de paso garantiza una alimentación fluida e ininterrumpida.

Selección de material (PS, PET, PC)

La elección del material afecta a la resistencia mecánica, la transparencia, la resistencia térmica y el comportamiento frente a ESD.

- Poliestireno (PS): Rentable, adecuado para el encapsulado estándar de IC

- Tereftalato de polietileno (PET): Transparente, ideal para sistemas de inspección óptica

- Policarbonato (PC): Resistencia a altas temperaturas para entornos exigentes

La selección del material adecuado depende de la sensibilidad del componente, las condiciones del proceso y los requisitos de inspección.

Protección contra ESD y humedad para chips semiconductores

Los dispositivos semiconductores son altamente sensibles a las descargas electrostáticas. Incluso eventos de ESD de bajo voltaje pueden causar defectos latentes difíciles de detectar durante la inspección, pero que provocan fallos en campo.

La cinta portadora para chips aborda esto mediante:

- Materiales conductivos: Proporcionan vías de disipación controlada

- Recubrimientos antiestáticos: Evitan la acumulación de carga durante la manipulación

Estas soluciones suelen integrarse en configuraciones de cinta portadora antiestática.

Consideraciones sobre sensibilidad a la humedad

Muchos encapsulados IC están clasificados según los Niveles de Sensibilidad a la Humedad (MSL), lo que significa que pueden absorber humedad del entorno. Una manipulación inadecuada puede provocar:

- Efecto popcorning durante el reflow

- Daño estructural interno

- Reducción de la fiabilidad del dispositivo

La cinta portadora funciona en combinación con embalaje en seco, desecantes y bolsas con barrera de humedad para proteger los componentes sensibles durante el almacenamiento y el transporte.

Problemas comunes en aplicaciones de cinta portadora para chips

Incluso con materiales de alta calidad, un diseño o una selección inadecuados pueden provocar problemas recurrentes en producción. Comprender estos problemas ayuda a identificar las causas raíz y prevenir pérdidas de rendimiento.

Rotación o desalineación del chip

Alveolos sobredimensionados o una geometría de cavidad deficiente pueden permitir que los chips roten o se desplacen dentro del alveolo. Esto conduce a una orientación incorrecta durante la recogida y a errores de colocación.

Problemas de alimentación en máquinas SMT

La inestabilidad en la alimentación suele estar causada por:

- Espaciado de paso inconsistente

- Orificios de arrastre desalineados

- Deformación de la cinta

Estos problemas interrumpen la sincronización entre el alimentador y el cabezal de colocación.

Problemas de pelado de la cinta de cobertura

La fuerza de pelado debe controlarse cuidadosamente. Si es demasiado alta, los componentes pueden levantarse o desplazarse; si es demasiado baja, se compromete la integridad del sellado.

Un pelado inestable puede provocar:

- Pérdida de componentes

- Componentes proyectados durante la operación a alta velocidad

- Aumento del tiempo de inactividad

Daños electrostáticos (fallos por ESD)

Sin una protección ESD adecuada, los chips pueden sufrir daños silenciosos que superan la inspección inicial pero fallan posteriormente en campo.

Cuando las soluciones estándar no pueden resolver estos problemas, muchos fabricantes recurren a diseños de cinta portadora personalizada para optimizar la geometría del alveolo, los materiales y el rendimiento.

Cinta portadora para chips estándar vs. personalizada: cuándo elegir cada opción

La selección entre cinta portadora estándar y personalizada depende del tipo de componente, el volumen de producción y los requisitos de calidad.

Cinta portadora estándar

- Menor coste y disponibilidad más rápida

- Adecuado para encapsulados de uso común (p. ej., SOP, SOT)

- Adecuado para aplicaciones de propósito general

Cinta portadora personalizada

- Diseñado para componentes únicos o de alto valor

- Dimensiones y tolerancias de cavidad optimizadas

- Mayor fiabilidad de alimentación y reducción de defectos

Las soluciones personalizadas son especialmente importantes para encapsulados semiconductores avanzados como QFN, BGA o IC de forma irregular.

Cómo seleccionar la cinta portadora para chips adecuada (paso a paso)

Elegir la cinta portadora para chips correcta requiere un proceso de evaluación estructurado.

Paso 1: Definir las dimensiones del componente

Mida con precisión la longitud, la anchura, el espesor y las tolerancias permitidas. Esto garantiza un diseño adecuado del alveolo y evita movimientos.

Paso 2: Determinar los requisitos del material

Considere:

- Sensibilidad a ESD

- Transparencia para inspección

- Resistencia térmica

Paso 3: Ajustar el tipo de encapsulado

Diferentes tipos de encapsulado requieren distintas geometrías de alveolo. Por ejemplo:

- Los encapsulados planos requieren cavidades poco profundas

- Los encapsulados de matriz de bolas requieren cavidades más profundas

Paso 4: Validar la fuerza de pelado

Asegúrese de que el pelado de la cinta de cobertura sea estable y consistente en todas las condiciones de producción. Esto afecta directamente al rendimiento de alimentación.

Paso 5: Realizar pruebas piloto

Antes de la producción a gran escala, pruebe la cinta en condiciones reales de SMT. Evalúe:

- Suavidad de alimentación

- Precisión de recogida

- Tasas de defectos

Trabajar con un proveedor que ofrezca soluciones integradas de embalaje en cinta y carrete puede agilizar este proceso de validación y reducir el riesgo de implementación.

Normativas del sector para cinta portadora para chips (EIA-481 explicado)

EIA-481 es la principal norma del sector que regula el embalaje en cinta y carrete para componentes electrónicos. Define parámetros críticos como:

- Ancho de la cinta y dimensiones de la cavidad

- Posicionamiento de los orificios de arrastre

- Tamaño y configuración de la bobina

El cumplimiento de EIA-481 garantiza la compatibilidad entre diferentes equipos SMT y cadenas de suministro globales. También minimiza problemas de integración al abastecerse de componentes de múltiples proveedores.

Para fabricantes y compradores, el cumplimiento de esta norma no es opcional: es esencial para mantener una calidad constante y la eficiencia operativa.

Conclusión: Por qué la calidad de la cinta portadora para chips afecta directamente al rendimiento

La cinta portadora para chips desempeña un papel mucho más crítico que el simple embalaje. Influye directamente en cómo se manipulan, alimentan y colocan los componentes durante el ensamblaje SMT.

La precisión en el diseño del alveolo, la selección de materiales y la protección ESD determina si la producción funciona sin problemas o sufre defectos recurrentes. Una cinta mal diseñada puede provocar desalineaciones, errores de alimentación y riesgos ocultos de fiabilidad.

Para componentes semiconductores de alto valor, invertir en soluciones de cinta portadora correctamente diseñadas es una forma práctica de reducir defectos, mejorar el rendimiento y garantizar la fiabilidad del producto a largo plazo.